DWM3001C

注解

要获取更多信息,请访问 Qorvo的 DWM3001C 页面.

主要功能

符合 IEEE 802.15.4-2015 和 IEEE 802.15.4z BPRF 标准

与 FiRa™ PHY, MAC 和认证开发完全一致

支持频道 5(6.5 GHz)和频道 9(8 GHz)

FCC, SRRC 和 ETSI 认证(计划中)

带有 BLE 收发器的 Nordic nRF52833 SoC

电源电压 VCC: 2.5 V - 3.6 V

蓝牙芯片天线

AES 128/256 安全块

全相干接收器,实现最大范围和精度

针对电池应用优化功耗

数据传输速率为 850 kbps, 6.8 Mbps

最大数据包长度为 1023 字节,用于高数据吞吐量应用

集成 MAC 支持功能

向后兼容 DWM1001C 模块

温度范围-40°C至+85°C

软件兼容性

它与 LEAPS RTLS 和 潘专业人士 都兼容.

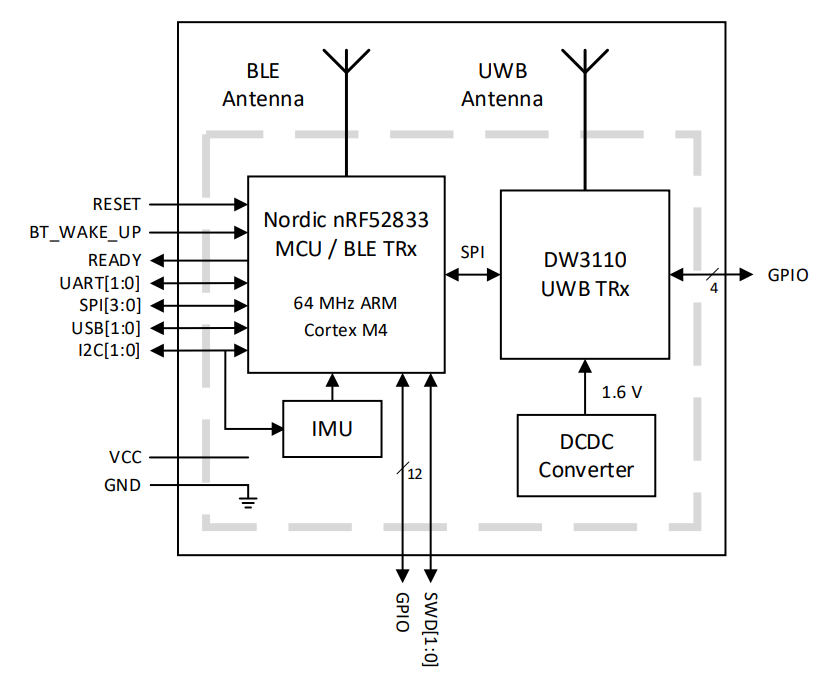

方框图

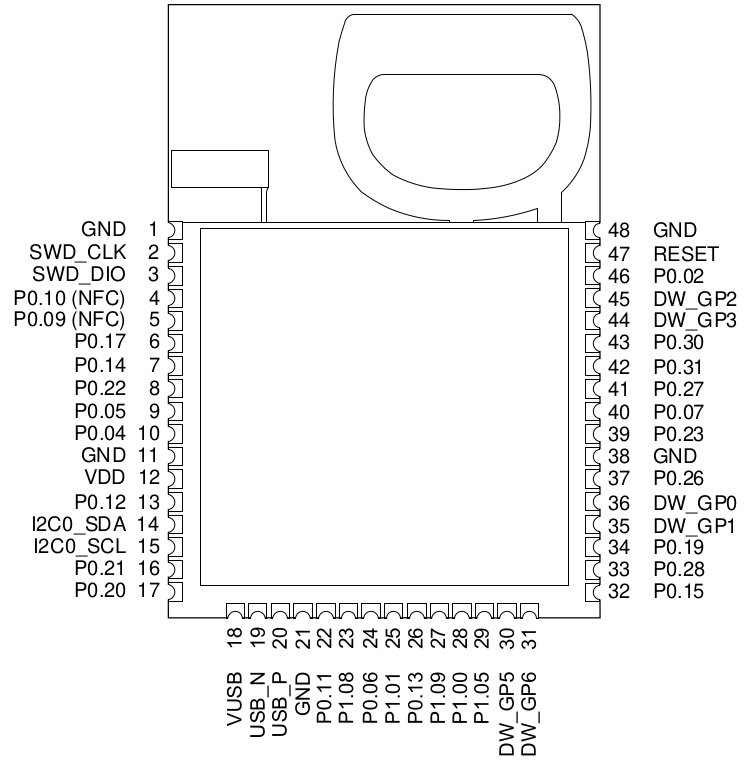

引脚说明

引脚编号

DWM3001C 模块的引脚分配如下(从上往下看):

引脚说明

信号名称 |

引脚 |

输入/输出 (默认) |

描述 |

集成电路引脚参考 |

|---|---|---|---|---|

数字接口 |

||||

SWD_CLK |

2 |

DI |

用于 nRF52833 处理器调试和编程的串行线调试时钟输入. |

[N] SWDCLK |

SWD_DIO |

3 |

DIO |

串行线调试输入/输出,用于 nRF52833 处理器的调试和编程. |

[N] SWDIO |

P0.10 (NFC2) |

4 |

混合 |

用于nRF52833处理器的通用I/O. NFC 天线连接. |

[N] P0.10 |

P0.09 (NFC1) |

5 |

混合 |

用于nRF52833处理器的通用I/O. NFC 天线连接. |

[N] P0.09 |

P0.17 |

6 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.17 |

P0.14 |

7 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.14 |

P0.22 |

8 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.22 |

P0.05 |

9 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.05 |

P0.04 |

10 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.04 |

P0.12 |

13 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.12 |

I2C0_SDA |

14 |

DIO |

nRF52833 处理器和 LIS12DH 加速计的 I2C 数据信号. |

[N] P0.24 |

I2C0_SCL |

15 |

DIO |

nRF52833 处理器 sand LIS12DH 加速计的 I2C 时钟信号. |

[N] P1.04 |

P0.21 |

16 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.21 |

P0.20 |

17 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.20 |

USB_N |

19 |

DIO |

nRF52833处理器的USB D-输入/输出. |

[N] D- |

USB_P |

20 |

DIO |

用于nRF52833处理器的USB D+输入/输出. |

[N] D+ |

P0.11 |

22 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.11 |

P1.08 |

23 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P1.08 |

P0.06 |

24 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.06 |

P1.01 |

25 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P1.01 |

P0.13 |

26 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.13 |

P1.09 |

27 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P1.09 |

P1.00 |

28 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P1.00 |

P1.05 |

29 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P1.05 |

DW_GP5 |

30 |

DIO |

用于DW3110收发器的通用输入/输出. |

[D] GPIO5 |

DW_GP6 |

31 |

DIO |

用于DW3110收发器的通用输入/输出. |

[D] GPIO6 |

P0.15 |

32 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.15 |

P0.28 |

33 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.28 |

P0.19 |

34 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.19 |

DW_GP1 |

35 |

DIO |

用于DW3110收发器的通用输入/输出. |

[D] GPIO1 |

DW_GP0 |

36 |

DIO |

用于DW3110收发器的通用输入/输出. |

[D] GPIO0 |

P0.26 |

37 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.26 |

P0.23 |

39 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.23 |

P0.07 |

40 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.07 |

P0.27 |

41 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.27 |

P0.31 |

42 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.31 |

P0.30 |

43 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.30 |

DW_GPIO3 |

44 |

DIO |

用于DW3110收发器的通用输入/输出. |

[D] GPIO3 |

DW_GPIO2 |

45 |

DIO |

用于DW3110收发器的通用输入/输出. |

[D] GPIO2 |

P0.02 |

46 |

DIO |

nRF52833 处理器的通用输入/输出. |

[N] P0.02 |

重置

(P0.18)

|

47 |

DIO |

用于nRF52833处理器的通用输入/输出. 低电平有效复位输入. |

[N] nRESET |

电源供应 |

||||

VDD |

12 |

P |

3 V电源引脚. |

|

地面 |

||||

GND |

1, 11,

21,

38, 48

|

G |

共同点. |

|

缩略语解释

缩写 |

解释 |

|---|---|

I |

输入 |

IO |

输入/输出 |

O |

输出 |

G |

地面 |

P |

电源 |

PD |

电源去耦 |

O-L |

默认为输出,重置后为低电平 |

O-H |

重置后默认为输出,高电平 |

I |

默认为输入. |

注解

任何后缀为‘n’的信号都表示低电平有效信号.